# Lab on a Chip

**View Article Online**

## PAPER

Check for updates

Cite this: Lab Chip, 2019, 19, 897

# Reliable interfaces for EGaIn multi-layer stretchable circuits and microelectronics<sup>†</sup>

Daniel Green Marques, <sup>(1)</sup><sup>a</sup> Pedro Alhais Lopes,<sup>a</sup> Anibal T. de Almeida, <sup>(1)</sup><sup>a</sup> Carmel Majidi<sup>b</sup> and Mahmoud Tavakoli <sup>(1)</sup>\*<sup>a</sup>

We tackle two well-known problems in the fabrication of stretchable electronics: interfacing soft circuit wiring with silicon chips and fabrication of multi-layer circuits. We demonstrate techniques that allow integration of embedded flexible printed circuit boards (FPCBs) populated with microelectronics into soft circuits composed of liquid metal (LM) interconnects. These methods utilize vertical interconnect accesses (VIAs) that are produced by filling LM alloy into cavities formed by laser ablation. The introduced technique is versatile, easy to perform, clean-room free, and results in reliable multi-layer stretchable hybrid circuits that can withstand over 80% of strain. We characterize the fabrication parameters of such VIAs and demonstrated several applications, including a stretchable touchpad and pressure detection film, and an allintegrated multi-layer electromyography (EMG) circuit patch with five active layers including acquisition electrodes, on-board processing and Bluetooth communication modules.

Received 15th October 2018, Accepted 28th January 2019

DOI: 10.1039/c8lc01093e

rsc.li/loc

## 1 Introduction

Stretchable circuits have been the focus of increasing attention during the last decade due to their applications in sensing,<sup>1-3</sup> wearable biomonitoring,<sup>4-6</sup> and soft robotics.<sup>7,8</sup> Despite rapid advances in fabrication of stretchable electronics, previous efforts have mainly focused on the development of stretchable interconnects and sensing architectures. However, the functionality of such systems remains ultimately dependent of solid-state technology (SST), from simple light emitting diodes (LEDs) to packaged integrated circuits (ICs) for data acquisition, processing and communication. Integrating such components introduces a drastic mechanical mismatch that is the cause of premature failure and/or loss of functionality. The challenge of interfacing stretchable electronics with rigid microelectronics is a key to further progress of this field. Typically such systems are composed of a stretchable polymer matrix - e.g. polydimethylsiloxane (PDMS) - and conductive stretchable interconnects. These can be achieved using conductive elastomers,9,10 deterministic architectures of metal traces patterned into meandered geometries,<sup>11-14</sup> or conductive composites relying on rigid conductive particles,<sup>15,16</sup> or nanotubes.<sup>17-19</sup>

Liquid metal (LM) offers another approach for engineering intrinsically stretchable and highly conductive interconnects. Among these alloys, eutectic gallium-indium (EGaIn) is popular since it is liquid at room temperature (melting point ~15.5 °C) and can therefore deform with surrounding materials without introducing significant mechanical resistance. Moreover, it has low-viscosity  $(1.99 \times 10^{-3} \text{ Pa s})$ ,<sup>20</sup> and negligible toxicity.<sup>21,22</sup> The rapid formation of a thin 'skinlike' surface oxide promotes rheological stability of EGaIn in microchannels, unlike liquid mercury which easily reflows, while it also avoids further oxidation by acting as a passivating layer.<sup>20</sup> As opposed to conductive composites whose conductivity relies on particle percolation, EGaIn exhibits higher conductivity  $(3.4 \times 10^6 \text{ S m}^{-1})$  and lower hysteresis. Its intrinsic stretchability doesn't depend on programmed shapes for prescribed elongations as it's the case for deterministic architectures. Research with EGaIn, Ga-In-Sn (Galinstan), and other Ga-based LM alloys includes soft microfluidic electronics,<sup>23</sup> micro- and nano-droplet suspensions,<sup>24</sup> and electrochemical manipulation.<sup>25,26</sup> Circuit fabrication methods include liquid metal injection,<sup>27-29</sup> laser patterning,<sup>30</sup> stencil deposition,<sup>31,32</sup> microcontact printing,<sup>33</sup> inkjet printing,<sup>34,35</sup> hydro-printing,<sup>36</sup> direct writing,<sup>37-41</sup> and bi-phasic alloys,<sup>42,43</sup> among others.

Recently, there has been increasing interest by researchers in the development of reliable interfacing between EGaInbased circuitry and packaged or unpackaged SST. Interfacing connections have been achieved using HCl vapor-treated EGaIn "solder",<sup>43</sup> and direct connection to a bare CMOS die.<sup>44</sup> Indirect integration uses flexible printed circuit boards

<sup>&</sup>lt;sup>a</sup> Institute of Systems and Robotics, University of Coimbra, Rua Silvio Lima-Polo II, 3030-290 Coimbra, Portugal. E-mail: mahmoud@isr.uc.pt

<sup>&</sup>lt;sup>b</sup> Integrated Soft Materials Lab, Carnegie Mellon University, Pittsburgh, PA 15213, USA

$<sup>\</sup>dagger$  Electronic supplementary information (ESI) available. See DOI: 10.1039/ c8lc01093e

#### Paper

(FPCBs),<sup>45</sup> or *z*-axis conductive films.<sup>46,47</sup> Multi-layer fluidic circuits have been previously achieved using injection,<sup>3</sup> although it is limited to two terminals (inlet and outlet) and requires a pre-structured elastomer matrix. Out-of-plane interconnects are also achieved by microfluid 3D printing<sup>48</sup> and four degrees-of-freedom direct writing,<sup>49</sup> although it is a time-consuming process and not compatible with scalable production.

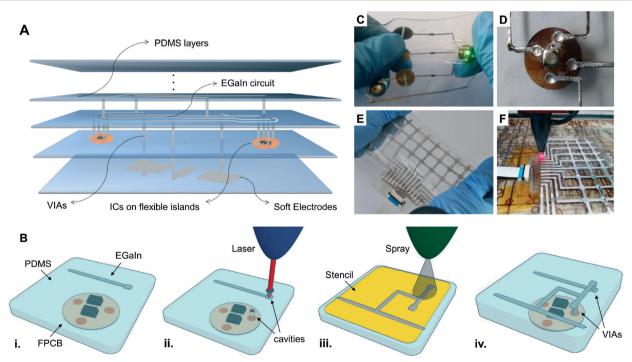

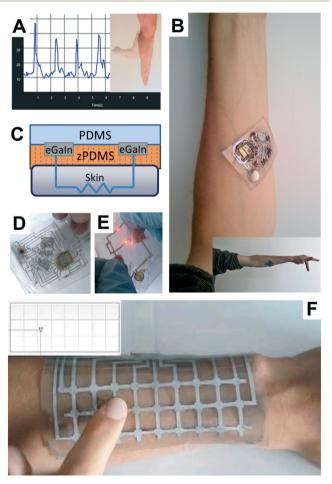

Here we present a novel technique for layer-by-layer fabrication of highly stretchable, compact, and multi-layer hybrid circuits based on LM interconnects and laser-ablated EGaIn filled VIAs, that allows reliable integration of SST microelectronics (Fig. 1) and EGaIn circuit layers. We show a semiautomated procedure for creating z-axis VIAs by forming cavities with laser ablation and then filling the cavities with liquid metals. VIAs serve as interlayer connections between EGaIn interconnects, as well as with copper traces through selective wetting. Incorporation of microelectronics in the patch is facilitated by the integration of thin polyimidecopper islands previously populated with silicon chips. The FPCBs can also be used as embedded terminals to connect with external electronic test equipment or power supplies. In this case, the VIAs eliminate the need to insert metallic wires in the fluidic terminals of the device for signal transmission, 50-52 which may impair functionality, since it lacks mechanical robustness and introduces the possibility of variable contact resistance and LM leakages. The developed method is clean-room free, low-cost and simple to replicate. Moreover, it is a step towards automated creation of multilayer stretchable circuitry thereby contributing to the miniaturization of the footprint of the circuit and scalability of production due to reliable integration of chips. We end the study by demonstrating multi-layer circuits that incorporate a RGB LED circuit, a stretchable capacitive touch and pressure detection film, and a fully integrated electromyography (EMG) patch for continuous monitoring of muscular activity. The wearable patch includes integrated electrodes, data acquisition, processing microelectronics, and Bluetooth wireless communication.

## 2 Results & discussion

#### 2.1 Fabrication work-flow

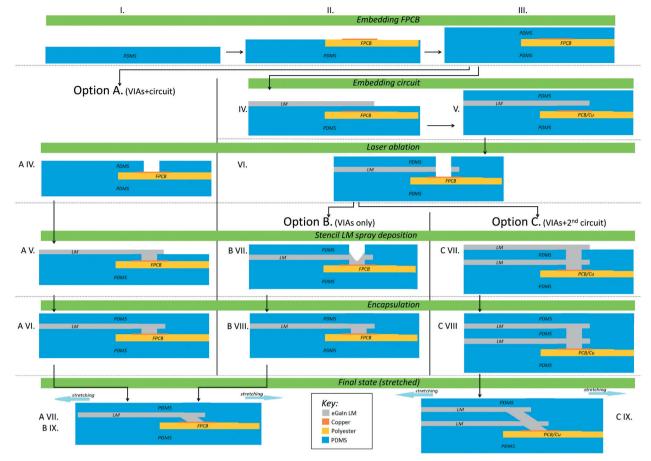

Referring to Fig. 2, the multi-layer interfaces fabrication approach is composed of the following processing steps: first, FPCB islands hosting soldered chips are placed over a halfcured PDMS film (I and II). Next, these islands are enclosed with a second layer of pre-elastomer (III). After curing, each of the Cu pads of the FPCBs is accessed by vertical laser ablation of the enclosing PDMS layer (A. IV). Afterwards, a previously laser patterned stencil is bonded over the cured PDMS, and EGaIn is spray coated over it. In this way not only one

**Fig. 1** A. Exploded view drawing of a multi-layer stretchable circuit with interfaced microelectronics and flexible islands with a bottom layer for soft electrodes. Additional layers and VIAs can be fabricated; B. fabrication of EGaln VIAs: (i.) once the flexible PCBs and EGaln interconnects are encapsulated in a stretchable elastomer (ii.) the selected traces and pads are accessed by vertical laser ablation (iii.) the cavities are filled with liquid metal when spray coating over a patterned stencil (iv.), which is removed before encapsulating the VIAs and the new circuit layer; C. stretchable circuit with multi-layer VIAs-based interfaces with a RGB LED soldered on a flexible island with copper pads (FPCB); D. detail view of the LED on a FPCB after simultaneous masked spray deposition of the EGaln circuit and VIAs; E. soft capacitive touchpad and pressure mapping film interfaced with an external processing unit; F. fabrication step of  $CO_2$  laser ablation prior to the deposition of EGaln VIAs.

**Fig. 2** Detailed flow of the processing steps for the creation of a multi-layer interfaces, showing possible variations: (A) simultaneous fabrication of VIAs and the circuit layer; (B) fabrication of VIAs with a previous embedded circuit layer; and (C) fabrication of VIAs and additional circuit layers besides the previous embedded circuit layer. In layer-by-layer manufacture, the FPCB is placed onto a half-cured PDMS substrate (I. and II.) and sealed (III.). Eventually a EGaIn circuit layer is embedded too (IV. and V.). Vertical laser ablation of the elastomer is used to access the bottom Cu layer on the FPCB and any intermediate EGaIn layers (VI. and A IV.). Spray masked deposition of EGaIn fills the VIAs and can create additional circuit layers (A V., B VIII. and C VIII.). Finally a top sealing layer of PDMS is applied to encapsulate the device (A VI., B VIII. and C VIII.). The interfaced system withstands applied stress and deformation (A VII., B IX. and C IX.).

layer of the circuit interconnects are produced, all of the created VIAs are filled with EGaIn, and the interface between the Cu pads of the FPCB and the EGaIn is established (A. V). Finally, the circuit is enclosed with a sealing layer of PDMS (A. VI).

Alternatively, VIAs can be created after enclosing a first EGaIn circuit layer (V.). This is particularly interesting for the creation of multi-layer circuits in which the access points of more than one circuit layer are aligned (C. IIX), which was used in the creation of the EMG circuit as it will be shown in the Applications section. Besides, in the proposed sequence of option B (B. V, VI, VII, IIX), VIAs are created and filled with EGaIn in a separate step. This can be advantageous over the previous method (option A), since here VIAs can be fabricated in a single final step of fabrication.

Multi-layer EGaIn circuits follow the same processing steps where the bottom layer is an EGaIn trace instead. The enclosed EGaIn is partially ablated and remains exposed around the ablation area. The subsequent deposited EGaIn is brought into contact with the exposed inner EGaIn layer connecting both layers together. When filling the VIAs by spray deposition, the thin EGaIn oxide skin likely ruptures and reshapes into a new interconnect that extends across insulating layers.

#### 2.2 Electromechanical characterization

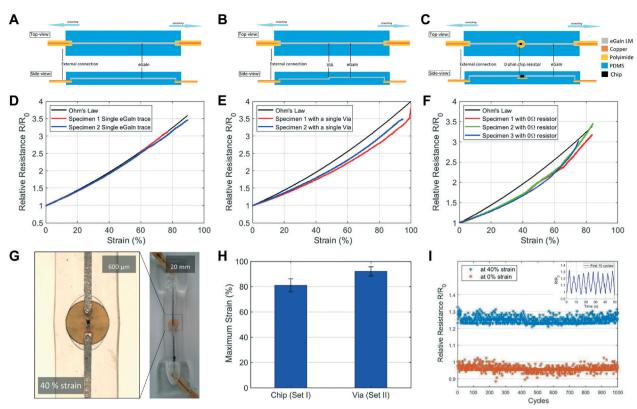

In order to demonstrate the performance of stretchable VIAs and interfaces, the electromechanical behavior is characterized under mechanical deformation. Three types of sample specimens were fabricated in a custom dog-bone shape. Further details on the dimensions of the specimens can be found in the ESI.† In set I, a reference type of sample composed of a single EGaIn trace running between both ends of the sample was tested, as it can be seen in the schematic drawings of Fig. 3A. In set II, a single VIA connects two EGaIn traces each ranging half of the length of the sample (Fig. 3B). In set III, a surface-mount 0-ohm chip resistor was interfaced with two straight EGaIn traces (Fig. 3C). Each EGaIn trace connects one end of the sample to one pad of the resistor through a VIA to a copper pad. More details on the Paper

**Fig. 3** Electromechanical characterization of dedicated samples under tensile loading. Top-view and cross-section schematic views of the specimens: A. EGaln reference sample (set I); B. single VIA connecting two EGaln traces (set II); C. SMD 0  $\Omega$  chip resistor interfaced with VIAs to EGaln traces (set III). Relative resistance and strain curve: D. set I; E. set II; F. set III; G. Specimen from set III and detail view of the delamination of a flexible island at 40% uniaxial strain. H. Stretchability of VIAs and interfaces. I. Under cyclic mechanical loading, the interfaced chips (set I) reliably maintain the range of variation over 1000 cycles at 40% and 0.4 Hz. Inset: To a stretch/release cycle corresponds an increase/decrease in resistance due to the EGaln interconnects.

fabrication can be found in the Materials and methods section. The specimens were then subject to uniaxial tensile loading and the electrical resistance across the sample was measured during the test.

Referring to Fig. 3D-F, we show the relative resistance as a function of strain for each type of samples. The percent elongation at break for set II and III was respectively 92.1 ± 3.7% and 81.1  $\pm$  5.1% (Fig. 3H), while for set I the highest recorded elongation was 100%. The stretchability of the interfaces is in the same range as previous EGaIn-based interface methods.43 For sets II and III, the change in resistance is slightly lower than the theoretical estimation based on the Ohm's law. This approximation, however, doesn't take into account the volume of EGaIn contained inside the VIA, which decreases the relative change in resistance under applied strain. Electrical failure occurs for all samples due to mechanical rupture of the elastomer at the middle of the specimen. For sets II and III, the rupture happens at the stress concentration zone of the non-stretchable to stretchable transition, which is at the rigid chip's edge or at the EGaIn VIA. The resistance of the samples with a single VIA connecting two 4.0 cm long EGaIn traces was 843.8  $\pm$  111.9 m $\Omega$  measured with a 4-wire measurement for 4 samples.

One of the general problems in LM-based interfaces under applied stress is the possible leakage of LM into voids created by delamination of the stretchable matrix from the rigid component. As the elastomer is not strongly bonded to the rigid inclusion they separate typically at above ~30% of elongation, possibly leading to the propagation of tearing within the elastomer. EGaIn leaks into these voids if they are connected to the EGaIn fluidic channels. However, for VIAsbased interfaces, it was observed as shown in Fig. 3G, that EGaIn leakage is prevented in the rigid-soft interface even under repeated deformation. To simulate repeated applied deformation, a cyclic loading tensile test was performed. VIAsbased interfaces withstand over 1000 cycles of mechanical loading up to 40% strain at a cycle rate of 0.4 Hz. Fig. 3I shows the relative resistance at 0% and 40% strain for each cycle, which remains in the same range through 1000 cycles, without signs of electrical degradation. Relative resistance cycles between 0.96 and 1.25, average values respectively at minimum and maximum strains. The standard deviations are 0.019 and 0.017 respectively. These interfaces can therefore remain functional while enduring high numbers of cycles without significant changes in resistance.

#### 2.3 Laser ablation

An infrared  $CO_2$  laser engraver (VLS 3.50, 10.6  $\mu$ m wavelength laser, 30 W, Universal Laser Systems) is used to ablate the

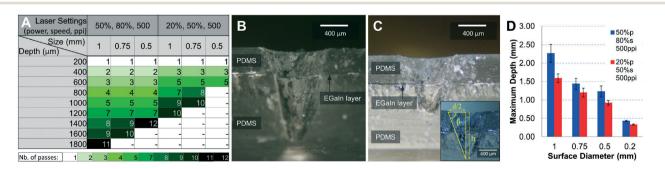

surface of the elastomer. The amount of ablated material depends on the energy transfer from the beam to the target surface. This energy can be controlled with the parameters of the laser printer: power (p), speed (s) and points per inch (ppi). Sequential laser printing also allows to incrementally increase the depth of ablation of the elastomer. In this process, as deeper layers are exposed, they become out of focus in regard to the initial focus plane of the beam. However, a high-power beam continues to ablate exposed surfaces farther from the focus zone. Therefore, the width of the ablated diameter narrows as the depth increases, creating a coneshaped ablated space (Fig. 4B).

Although the power and speed parameters can be used to control the ablation depth, high energy beams (high powers and low speeds) tend to create burnt remains inside the ablated space. Instead, ablation can be performed at lower energy density, with several repetitions. Hence, rather than varying the energy of the beam, depth control can be easily achieved based on the repetition of the ablation. To determine the number of passes required to reach certain depths, three different settings were tested in a laser engraver: setting 1 (50% p 80% s 500 ppi), setting 2 (20% p 50% s 500 ppi), and setting 3 (5% p 15% s 500 ppi). More details of the experimental protocol can be found in the Materials and methods section. Fig. 4A summarizes the results for settings 1 and 2. It shows the number of passes needed to ablate an EGaIn layer at a certain depth inside PDMS. The distance between EGaIn layers is 200 µm. Although setting 3 didn't cause significant ablation, even after repeated printing, a wide range of set parameters can be used, changing the dependency of depth with the number of passes. Here we report 1.0 mm wide VIAs reaching a 1800 µm deep layer after 11 sequential printings, and 1400 µm in 12 repetitions for 0.5 mm wide VIAs (Fig. 4A) for setting 1.

To understand the maximum depth dependency with the laser parameters and size of the VIAs, the cross section of the laser ablated space was evaluated by optical microscopy. The angle of the cone-shaped ablation was measured for different VIAs sizes and two sets of laser parameters. Fig. 4D shows the theoretical estimation of the maximum depth using a simple triangle model on the cone's cross section, as it is shown in the inset of Fig. 4C. The angle  $\beta$  of the cone's base was measured for five samples per top diameter *d* and per laser setting. The depth *h* is determined by the relation  $h = \frac{d}{2} \tan \beta$ . The predictions agree with the experimental re-

$\eta = \frac{1}{2} \tan \beta$ . The predictions agree with the experimental re-

sults in Fig. 4A with an average difference of 229  $\mu$ m, which is comparable with the uncertainty of the experimental data. Furthermore, we can conclude that the base angle doesn't depend on the top diameter but it is higher for setting 1 than for setting 2. That it, the base angle increases for higher beam energies. This follows what is expected, as the energy of the beam on a point that is out of focus, while being lower than in the focal area, is still enough to cause the ablation of the material. It follows that lower beam energy results in a sharper cone shape and for these cones, a wider diameter corresponds to greater VIA depth.

#### 2.4 Interfacing methods: a comparison

Different materials and fabrication methods typically require different interfacing methods. Here, the performance of VIAsbased interfacing is compared to the results of previous methods. Table 1 summarizes the performances of some notable interfacing methods. Xu et al.13 reported a biomonitoring patch with wavy metal interconnects free-floating in a fluidic matrix that withstand up to 40% strain up to collision of the rigid chips. Robinson, et al.53 studied the deformable-non-deformable interfaces an proposed the inclusion of flexible polyimide islands under the chips, which connect with a thin-film of gold and remains functional only up to 20% strain before the cracks on the thin-film break the conductive path of the interconnects. Bossuyt, et al.14 developed a scalable manufacturing method of hybrid circuits using deterministic interconnects over a flexible polyimide substrate designed for 10-15% strain. Ozutemiz, et al.43 proposed a method for fabrication of EGaIn circuits directly interfacing the pins of packaged chips, which besides reaching over 80% maximum strain, withstands 2000 cycles

Fig. 4 A. Number of passes to reach a range of depths from 200 to 1800  $\mu$ m for different ablation surface diameters (size) and laser ablation settings. Microscope view of the cross section of the ablation result for the same number of passes for laser settings 1 and 2 and different surface sizes, presenting its typical cone-shape: B. 50% power, 80% speed, 500 ppi, 1.0 mm top diameter. On successive passes the laser ablates areas out of the beam focus. C. 20% power, 50% speed, 500 ppi, 0.75 mm top diameter. D. Estimated maximum depth for four different surface diameters and for two sets of laser parameters. The VIA's cone-shape narrows faster for low-energy beams and wider VIAs can reach higher depths.

| Article                                         | Main feature                  | Type of interconnects           | Interfaces structure | Stretchability | Endurance              | Failure mode                    |

|-------------------------------------------------|-------------------------------|---------------------------------|----------------------|----------------|------------------------|---------------------------------|

| Xu, et al. (2011) <sup>13</sup>                 | Clean-room<br>fabrication     | Deterministic and free-floating | Single-layer         | 40%            | 6000 at 30%,<br>0.6 Hz | Collision of chips              |

| Robinson, <i>et al.</i> $(2014)^{53}$           | Flexible polyimide<br>islands | Thin-film gold                  | Single-layer         | 20%            | 1000 at 20%            | Broken interconnects            |

| Bossuyt, <i>et al.</i> $(2013)^{14}$            | Scalable                      | Deterministic copper            | Single-layer         | 15%            | 3500 at 10%,<br>0.4 Hz | Pre-designed for 15% max strain |

| Ozutemiz, <i>et al.</i><br>(2018) <sup>43</sup> | Direct interfacing            | Liquid metal (EGaIn)            | Single-layer         | 82.6 ± 13.3%   | 2000 at 40%,<br>0.1 Hz | PDMS rupture                    |

| Present work                                    | VIAs-based<br>interfacing     | Liquid metal (EGaIn)            | Multi-layer          | 81.1 ± 5.1%    | 1000 at 40%,<br>0.4 Hz | PDMS rupture                    |

from 5% to 40% at 0.1 Hz cyclic rate, showing only a slightly decreasing conductivity in the first hundreds of cycles.

Table 1

Comparison of interfacing methods in hybrid stretchable electronics

The present interfacing method combines EGaIn microfluidics for high stretchability (81.1  $\pm$  5.1%) with VIAs-based interfaces for multi-layer circuits with embedded microelectronics, integrated biosensing electrodes, complex circuitry. While further tests should be conducted to determine the fatigue life of the interfaces for a higher number of loading cycles, the present results show only a slight variation over the first 1000 cycles from 0% to 40% strain at 0.4 Hz. Another feature of this fabrication technique is that it enables robust electrical interfacing with FPCBs. This represents an important step toward scalable production, since chips can be soldered to the FPCBs with traditional methods, thus allowing their facile integration into the LM circuits. FPCBs provide excellent interface with LM, since EGaIn selectively wets copper and does not lose its electrical connection with the Cu during the strain. Moreover, in the case of low pitch SMD components, FPCBs allow creation of a larger pin out, thus allowing integration of dimensionally demanding chips.

## **3** Applications

#### 3.1 LED implementation

Following the method detailed in Fig. 2 (option A), the EGaIn circuit with VIAs was fabricated with a three-color RGB LED embedded into the PDMS matrix (Fig. 1A). Each of the RGB LED light outputs is activated by pressing a soft button made out of *z*PDMS using a conductive probe. A double-layer circuit with surface-mount LEDs was also fabricated, where each LED is directly placed onto a different circuit layer (Fig. 5E). When applied over separated EGaIn traces, the *z*PDMS film allows for the probe to bridge the columns over the traces and close the circuit (Fig. 5C), thus enabling current to flow through the LED.

## 3.2 External interfaces: dual-mode touchpad and pressure mapping film

While in some cases it is important to integrate directly the microelectronics chips in the stretchable circuit, in others it is preferred to interface them with external processing circuits. This includes for instance pressure mapping films. Nevertheless, a reliable interface between the stretchable sensor patch and rigid PCBs, prototyping boards or electronic test equipment is required. Here we demonstrate a soft capacitive touchpad, activated by the pressure or

**Fig. 5** A. EMG signal from a repetitive hand gesture transmitted to a computer application (ESI,† Video); B. all-integrated EMG patch on the forearm. Inset: Adhesion of the EMG patch to the skin while performing a hand gesture; C. cross-view of a *z*-axis conductive PDMS<sup>47</sup> and schematic of the electrical path connecting the separate EGaIn traces and a conductive surface for soft electrodes or buttons; D. EMG patch seen from the bottom; E. double-layer LED circuit with a coin cell battery and a *z*PDMS button, each LED is on a different circuit layer; F. humanmachine interaction with a soft touchpad placed on a volunteer's forearm to control a display which shows the point of pressure of the finger. The device uses VIAs to interface with the computer.

proximity of a finger, connected to an external prototyping board for capacitive sensing measurements (Fig. 1C and 5F). The interface is achieved by following the present fabrication technique and connecting the EGaIn traces to the embedded FPCB with VIAs (Fig. 1D). The FPCB contains a flat cable connector for signal transmission to the board. More details on the fabrication can be found in the Materials and methods section.

#### 3.3 All-integrated stretchable EMG patch

In order to demonstrate an all-integrated stretchable patch, we designed and developed a multi-layer stretchable patch for EMG monitoring (Fig. 5B and D), which is composed of bio-potential measurement skin contact electrodes, as well as data acquisition, filtering, processing and communication microelectronics. It is composed of 5 active layers with separating insulating layers of PDMS, and an overall of 10 thin stacked layers (Fig. 1E). PDMS layers were applied using a drop casting method, although spray deposition of silicon elastomer<sup>2</sup> could be studied to further minimize the insulator thickness. As a result of a bottom-to-top thin layer-by-layer fabrication, its total dimensions are  $47 \times 57 \times 2.7$  mm. Soft electrodes made of z-axis conductive PDMS (zPDMS)<sup>47</sup> are in contact with the human skin to acquire the bio-potential of the muscle's activity (Fig. 5A). In addition, having a layer for silicon chips and three wiring layers, the EMG patch is able to measure muscular activities (ESI† Video) and can be used to detect the human hand gesture.<sup>54</sup> Details on the fabrication can be found in the Materials and methods section. This approach to bioelectronic sensing represents a promising alternative to other techniques that incorporate hydrogels with EGaIn leads<sup>55</sup> as well as direct application of EGaIn to skin.<sup>56</sup> Further research remains in comparing the signal quality and electrical impedance associated with these different electrode architectures.

## 4 Materials and methods

#### 4.1 Materials

Polydimethylsiloxane (PDMS) was prepared in 10:1 base-tocuring agent weight ratio (Sylgard 184, Dow Corning). Thin layers of PDMS were fabricated using a thin film applicator (ZUA 2000 Universal Applicator, Zehntner GmbH). Gallium indium eutectic alloy (EGaIn) was prepared by mixing Ga and In, 75.5% and 24.5% by weight, respectively. The circuits and VIAs were deposited using EGaIn spray-coating and a patterned stencil mask. Stencil patterning, FPCB outline cut, and VIAs ablation were made with a CO<sub>2</sub> laser (VLS 3.50, 10.6 µm wavelength, 30 W, Universal Laser Systems). Thin flexible FPCBs were prepared with copper-clad (FR8515R, 25 µm Kapton, 25 µm adhesive, DuPont Pyralux). The zPDMS for the soft buttons and the electrodes was fabricated with 40% wt% of Ag-coated Ni microparticles 15 µm in diameter (69.5% Ni-30.5% Ag by wt, SN15P30, Potters Inc.).47 As the skinadhesive layer of the EMG, Silbione RT 4147 Gel (parts A and B mixed 1:1 by weight ratio), was used.

#### 4.2 Flexible printed circuit boards

First, the circuit pattern is printed on the copper surface using a wax printer (ColorQube 8580, Xerox). Then the exposed copper is etched in a bath of aqueous hydrochloric acid solution (30% concentration of HCl) diluted in hydrogen peroxide in a 1:2.5 vol% ratio for 1 min 30 s. The boards are rinsed with water, the wax is brushed off the copper traces and they are finally cleaned with acetone.

#### 4.3 Fabrication of tensile test specimens

The tensile test specimens were fabricated in a custom dogbone shape. The dimensions can be found in the ESI.<sup>†</sup> The fabrication steps follow a layer-by-layer procedure as presented in this paper. On a flat acrylic plate  $(20 \times 30 \text{ cm})$ 8 samples are fabricated simultaneously.

For set III: first, a 750 µm thick PDMS film is half-cured in the oven at 100 °C for 5 min 50 s. The acrylic plate is aligned at the corner of the laser and visual alignment guide marks are printed on the PDMS surface using the laser at 10% power (p), 75% speed (s), 500 ppi. One FPCB with a straight copper trace is manually placed at each end of each sample over the printed marks. Once the sample is prepared, it will enable external test wires to be connected. Each 0  $\Omega$  resistor soldered to a FPCB island is placed over its mark at the center of each sample. Then a 250 µm thick PDMS layer is applied over the previous PDMS layer and FPCBs and cured at 100 °C for 30 min. Having removed it from the oven, the plate is placed at the same corner of the laser machine for the ablation step, using 5 passes at 50% p, 80% s, 500 ppi. The stencil is laser cut separately and then applied over the PDMS aligned with the ablation points for the VIAs. The EGaIn traces and VIAs are fabricated with spray deposition of EGaIn over the patterned mask. After removing the stencil a final 500 µm thick PDMS layer is applied and cured at 100 °C for 1 h 45 min. Once it is removed from the oven, it cools down at room temperature during 10 min. The PDMS film is peeled off from the acrylic plate parallel to the direction of the traces and is placed over a metal plate. The outline of the dog-bone shape is cut in one pass at 100% p, 10% s, 1000 ppi. Any dust residues are cleaned off from the sample with a humid cloth. Acrylic tabs are glued to the ends of each sample using a silicon adhesive (Sil-Poxy™, Smooth-On) and dried for at least 12 h prior to testing.

For set II: first, a 300  $\mu$ m thick PDMS film is applied and half-cured on an acrylic plate in an oven at 100 °C for 5 min 40 s. After aligning the plate with the corner of the laser machine, the visual marks are printed on the PDMS surface using the same set of parameters as for set III. The FPCBs with a straight copper trace are then placed on the position of the marks at both end of each sample and another 300  $\mu$ m layer of PDMS is applied and cured at 100 °C for 30 min. The plate is aligned in the laser for the ablation of the VIAs over one of the connectors per sample. The stencil is cut separately and then placed over the PDMS. The first layer of traces and VIAs is spray-deposited. The EGaIn trace runs from the

#### Paper

VIA at the connector to the center of the sample. A third 300  $\mu$ m layer of PDMS is applied and cured. In the next step, the plate is aligned and the VIAs are ablated in 5 passes to reach the connector at the other end of each sample and in 2 passes to reach the enclosed EGaIn trace, using the same laser settings as in the fabrication of set III. Afterwards, using a new stencil the traces and VIAs are deposited, and a final 600  $\mu$ m layer of PDMS is applied and cured at 100 °C for 1 h 45. After laser cutting in a dog-bone shape, as for Set III, the tabs are glued and dried.

For set I: as for the sets I and II, a 300  $\mu$ m PDMS film is applied and half-cured. Laser marks are printed on the PDMS surface and straight FPCB connector are placed over the respective marks at both ends of each sample. After a 450  $\mu$ m PDMS layer is applied and cured, VIAs are ablated over the connector pad at each end of the samples. The patterned stencil is applied, and the EGaIn trace is deposited, connecting both ends of each sample. A 750  $\mu$ m PDMS layer is applied and cured, and as for sets III and II, after laser cutting in a dog-bone shape, the tabs are glued and dried.

#### 4.4 Tensile tests

The test specimens were subject to uniaxial tensile loading on a universal testing system (5969 Dual Column Tabletop, Instron). The load, displacement and electrical resistance were recorded using a voltage divider circuit and a DAQ (NI USB-6002, National Instruments). The strain was applied at a rate of 50 mm min<sup>-1</sup> up to the failure of the specimen.

Cyclic mechanical loading tests were conducted using a custom set-up that allows higher frequency testing. Controlled by an Arduino (Arduino MEGA 2560) with a RAMPS 1.4 Controller Shield, a stepper motor (Model 42BYGHW811) is connected to a screw rod that moves a 3D printed arm with laser cut acrylic grips where the sample is fixed at one end, while the other end is gripped in the fixed arm of the set-up. The analog acquisition circuit performs a 4-wire resistance measurement using a constant current supply and a instrumentation amplifier to measure the voltage drop across the sample. The acquisition is synchronized with the arm's displacement. The circuit diagram and more details can be found in the ESL<sup>†</sup>

#### 4.5 Double-layer circuit fabrication

Masked spray deposition of EGaIn over a thin PDMS film creates a single-layer pattern of interconnects. A battery and a LED directly placed over the EGaIn traces assemble a complete LED circuit, with an additional *z*PDMS button. Vertical laser ablation enables access to the inner EGaIn layer on two different points of the circuit. The inclusion of a small FPCB island with a straight copper track overlapped by the EGaIn trace was used to showcase the versatility of EGaIn VIAs. The subsequent spray deposition of EGaIn creates the second circuits layer and achieves the VIAs to the circuit layer below. After the second LED is directly connected to the second-layer EGaIn traces, the two-layer circuit is sealed with a final layer of PDMS.

#### 4.6 Single-island LED fabrication

The four terminal surface-mount LED (Cree PLCC4 3-in-1 SMD LED CLV1A-FKB,  $3.2 \times 2.8 \times 1.9$  mm) was soldered to a FPCB designed with additional pads to contact with the VIAs. After cutting the outline of the FPCB in a rounded shape, it was placed over a half-cured thin PDMS film and covered with a PDMS layer. Once the vertical laser ablation was made over the copper pads, the circuit and the VIAs to the pads of the FPCB were simultaneously deposited. Additional surfacemount 330  $\Omega$  resistors, as well as a coin cell battery, were directly placed on the EGaIn traces. The soft buttons were created using *z*PDMS over open EGaIn traces, to selectively close the circuit and activate each of the three LED output colors independently.

#### 4.7 Touchpad fabrication

Composed of 9 rows and 3 columns, the soft keyboard has 27 sensors. The conductive traces are deposited over a cured PDMS substrate and are then sealed with a second layer of PDMS. This process is repeated to achieve two encapsulated conductive layers totally insulated by a PDMS layer. The FPCB was prepared with a copper pad for each of the 12 outputs of the touchpad, and at the other end the pitch of the traces is adapted so that a flat cable connector (FCC) can be soldered. The FPCB is placed underneath the soft keyboard and the copper pads aligned with the EGaIn traces above. Laser ablation is performed and EGaIn VIAs are deposited, connecting each trace to the copper pad underneath. Finally, a thin layer of PDMS is applied to seal the VIAs and to bond both parts together.

#### 4.8 EMG fabrication

The fabrication of the soft EMG also follows a bottom-to-top layer-by-layer approach. First, a 250 µm PDMS layer is applied and cured on an acrylic plate. It is aligned in the laser machine to cut a 30 × 20 mm outline of a PDMS film which is then peeled off. In that area a zPDMS layer (25 wt% Ag-Ni particles) is cast and cured with a magnet below the acrylic plate to create the vertical conductive columns through the film. Using a laser patterned mask, spray-deposition of EGaIn shapes the electrodes over the zPDMS. When the covering PDMS layer is half-cured, visual alignment marks are laser printed and the FPCBs hosting packaged ICs are placed over the marks on the half-cured PDMS. PDMS is diluted in hexane (1:1 vol) and is then drop cast to form an insulating coating layer. After curing, vertical ablation is performed to reach the copper pads of the FPCBs and the enclosed EGaIn electrodes. Afterwards, EGaIn is spray-deposited creating the VIAs and the first circuit layer. A covering layer of PDMS is once again applied and cured. Again, vertical ablation is performed to reach the desired EGaIn traces and copper pads below. EGaIn spray deposition creates the second circuit layer

and the VIAs. This process is repeated for the third and last EGaIn circuit layer. A final layer of PDMS is applied and cured to encapsulate the circuit. Lastly, after the device is peeled off from the acrylic plate, a gel adhesive is selectively drop-casted on the bottom surface for skin adhesion.

#### 4.9 Maximum depth of ablation

To estimate the depth of the ablated space in function of the number of passes of the laser, EGaIn layers were enclosed in PDMS, 200 µm apart from each other in the z-axis direction. The number of repeated ablation steps was recorded when a given EGaIn layer had been exposed. The resolution of the depth versus the number of passes is therefore defined by the spacing of the layers in the z-axis direction. The ablation depth may be higher than the depth of the ablated EGaIn layer, but it is nevertheless smaller than the next deeper layer. Because each EGaIn layer was on a different xy-plane position, it was possible to test different laser parameters, ablation surface sizes and number of passes simultaneously. The sizes of the circular ablation features were 1.0, 0.75, 0.5 and 0.2 mm. The experiment was performed with five identical sample circles per each of the four different surface diameters, incrementally increasing the number of repetitions. Also, all sizes were tested with three different laser parameters of power (p), speed (s) and ppi: 50% p 80% s 500 ppi; 20% p 50% s 500 ppi; and 5% p 15% s 500 ppi. In order to evaluate at the optical microscope (SPZT-50, Carton) the cross-sections of the ablated features, a sharp razor was used to cut them along their diameter. The angle of the lateral face of the cone-shaped ablation spaces was measured with an image processing and analysis software (ImageJ) using the pictures taken with a photo camera (pentax K-3, Ricoh) mounted on the microscope.

## 5 Conclusions

We present a method to fabricate liquid metal VIAs for multilayer circuits based on EGaIn interconnects. The method uses a CO<sub>2</sub> laser to easily reach and expose inner LM layers encapsulated in PDMS by ablating the elastomer. Masked spray deposition of EGaIn fills all the VIAs thereby connecting different conductive layers. The result is a highly stretchable VIA  $(92.1 \pm 3.7\%)$  integrated in additive manufacturing of stretchable electronics based on liquid metals. Moreover, EGaIn VIAs can be used to interface with microelectronics. By embedding thin flexible copper laminates (FPCB) hosting solid state components, EGaIn circuits are connected to patterned Cu pads. Electromechanical tests show a stretchability of 81.1  $\pm$  5.1% and an ability to support 1000 loading cycles without significant change in the electrical properties of the interfaces or any LM leakage. We showed proof-of-concept applications including simple multi-layer LED circuits. As a general method to interface with external processing units and electronic test equipment, a stretchable keyboard was also demonstrated. Finally, to show the concept in an allintegrated scheme, we designed and developed a muscular monitoring (EMG) patch, which integrates bio-potential measurement electrodes, data acquisition, amplification, processing and communication microelectronics. Further work will focus on studying the integration of stretchable VIAs to interface other conductive materials and combine with different EGaIn deposition techniques, the automation and selfalignment of the fabrication method, and further development of multi-layer biomonitoring applications.

## Conflicts of interest

There are no conflicts to declare.

## Acknowledgements

This work was partially supported by the Foundation of Science and Technology of Portugal through the CMU-Portugal project Stretchtronics (CMUP-ERI/TIC/0021/2014), Dermotronics, (CENTRO-01-0145-FEDER-031784), and PAMI (CENTRO-01-0145-FEDER-022158) supported by FEDER through "Programa Operacional Regional do Centro" and National funds of FCT.

### Notes and references

- 1 E. L. White, J. C. Case and R. K. Kramer, *Sens. Actuators, A*, 2017, 253, 188–197.

- 2 M. Varga, C. Ladd, S. Ma, J. Holbery and G. Troster, *Lab Chip*, 2017, 17, 3272–3278.

- 3 Y. L. Park, B. R. Chen and R. J. Wood, *IEEE Sens. J.*, 2012, 12, 2711–2718.

- 4 J. A. Rogers, CLEO: Science and Innovations, 2017, p. SW1K-1.

- 5 Y. Chu, J. Zhong, H. Liu, Y. Ma, N. Liu, Y. Song, J. Liang, Z. Shao, Y. Sun, Y. Dong, X. Wang and L. Lin, *Adv. Funct. Mater.*, 2018, 28, 1803413.

- 6 M. D. Bartlett, E. J. Markvicka and C. Majidi, Adv. Funct. Mater., 2016, 26, 8496–8504.

- 7 R. P. Rocha, P. A. Lopes, A. T. de Almeida, M. Tavakoli and C. Majidi, *J. Micromech. Microeng.*, 2018, 28, 034001.

- 8 M. Tavakoli, P. Lopes, J. Lourenço, R. P. Rocha, L. Giliberto, A. T. de Almeida and C. Majidi, *IEEE Sens. J.*, 2017, 17, 5669–5677.

- 9 H. Stoyanov, M. Kollosche, S. Risse, R. Waché and G. Kofod, *Adv. Mater.*, 2013, 25, 578–583.

- 10 Y. Wang, C. Zhu, R. Pfattner, H. Yan, L. Jin, S. Chen, F. Molina-Lopez, F. Lissel, J. Liu, N. I. Rabiah, Z. Chen, J. W. Chung, C. Linder, M. F. Toney, B. Murmann and Z. Bao, *Sci. Adv.*, 2017, 3, e1602076.

- 11 D.-H. Kim, N. Lu, R. Ma, Y.-S. Kim, R.-H. Kim, S. Wang, J. Wu, S. M. Won, H. Tao, A. Islam, K. J. Yu, T.-I. Kim, R. Chowdhury, M. Ying, L. Xu, M. Li, H.-J. Chung, H. Keum, M. McCormick, P. Liu, Y.-W. Zhang, F. G. Omenetto, Y. Huang, T. Coleman and J. A. Rogers, *Science*, 2011, 333, 838–843.

- 12 M. D. Bartlett, E. J. Markvicka and C. Majidi, *Adv. Funct. Mater.*, 2016, 26, 8496–8504.

- 13 S. Xu, Y. Zhang, L. Jia, K. E. Mathewson, K.-I. Jang, J. Kim, H. Fu, X. Huang, P. Chava, R. Wang, S. Bhole, L. Wang, Y. J.

Na, Y. Guan, M. Flavin, Z. Han, Y. Huang and J. A. Rogers, *Science*, 2014, 344, 70–74.

- 14 F. Bossuyt, T. Vervust and J. Vanfleteren, *IEEE Trans. Compon., Packag., Manuf. Technol.*, 2013, 3, 229–235.

- 15 A. Larmagnac, S. Eggenberger, H. Janossy and J. Vörös, *Sci. Rep.*, 2014, 4, 7254.

- M. Tavakoli, R. Rocha, L. Osorio, M. Almeida, A. de Almeida, V. Ramachandran, A. Tabatabai, T. Lu and C. Majidi, *J. Micromech. Microeng.*, 2017, 27, 035010.

- 17 D. J. Lipomi, M. Vosgueritchian, B. C.-K. Tee, S. L. Hellstrom, J. A. Lee, C. H. Fox and Z. Bao, *Nat. Nanotechnol.*, 2011, 6, 788.

- 18 H.-C. Jung, J.-H. Moon, D.-H. Baek, J.-H. Lee, Y.-Y. Choi, J.-S. Hong and S.-H. Lee, *IEEE Trans. Biomed. Eng.*, 2012, 59, 1472–1479.

- 19 V. Martinez, F. Stauffer, M. O. Adagunodo, C. Forro, J. Vörös and A. Larmagnac, *ACS Appl. Mater. Interfaces*, 2015, 7, 13467–13475.

- 20 M. D. Dickey, R. C. Chiechi, R. J. Larsen, E. A. Weiss, D. A. Weitz and G. M. Whitesides, *Adv. Funct. Mater.*, 2008, 18, 1097–1104.

- 21 CRC Handbook of Chemistry and Physics, ed. J. R. Rumble, CRC Press/Taylor & Francis, Boca Raton, FL, 98th edn, (Internet Version, 2018).

- 22 J. Chandler, H. Messer and G. Ellender, *J. Dent. Res.*, 1994, 73, 1554–1559.

- 23 M. D. Dickey, Adv. Mater., 2017, 29, 1606425.

- 24 N. Kazem, T. Hellebrekers and C. Majidi, *Adv. Mater.*, 2017, 29, 1605985.

- 25 C. B. Eaker and M. D. Dickey, *Appl. Phys. Rev.*, 2016, 3, 031103.

- 26 J. Wissman, M. D. Dickey and C. Majidi, *Adv. Sci.*, 2017, 4, 1700169.

- 27 S. Cheng and Z. Wu, Lab Chip, 2012, 12, 2782-2791.

- 28 Y.-L. Park, C. Majidi, R. Kramer, P. Bérard and R. J. Wood, J. Micromech. Microeng., 2010, 20, 125029.

- 29 A. Fassler and C. Majidi, Lab Chip, 2013, 13, 4442-4450.

- 30 T. Lu, L. Finkenauer, J. Wissman and C. Majidi, *Adv. Funct. Mater.*, 2014, 24, 3351–3356.

- 31 J. Wissman, T. Lu and C. Majidi, *2013 IEEE SENSORS*, 2013, pp. 1–4.

- 32 S. H. Jeong, A. Hagman, K. Hjort, M. Jobs, J. Sundqvist and Z. Wu, *Lab Chip*, 2012, 12, 4657–4664.

- 33 A. Tabatabai, A. Fassler, C. Usiak and C. Majidi, *Langmuir*, 2013, 29, 6194–6200.

- 34 G. Li, X. Wu and D.-W. Lee, Lab Chip, 2016, 16, 1366–1373.

- 35 M. Tavakoli, M. H. Malakooti, H. Paisana, Y. Ohm, D. Green Marques, P. Alhais Lopes, A. P. Piedade, A. T. de Almeida and C. Majidi, *Adv. Mater.*, 2018, 30, 1801852.

- 36 P. A. Lopes, H. Paisana, A. T. De Almeida, C. Majidi and M. Tavakoli, ACS Appl. Mater. Interfaces, 2018, 10(45), 38760–38768.

- 37 Y. Zheng, Z.-Z. He, J. Yang and J. Liu, *Sci. Rep.*, 2014, 4, 4588.

- 38 Q. Wang, Y. Yu, J. Yang and J. Liu, Adv. Mater., 2015, 27, 7109-7116.

- 39 J. W. Boley, E. L. White, G. T.-C. Chiu and R. K. Kramer, Adv. Funct. Mater., 2014, 24, 3501–3507.

- 40 C. Ladd, J.-H. So, J. Muth and M. D. Dickey, *Adv. Mater.*, 2013, 25, 5081–5085.

- 41 A. Gannarapu and B. A. Gozen, *Adv. Mater. Technol.*, 2016, 1, 1600047.

- 42 A. Hirsch, H. O. Michaud, A. P. Gerratt, S. de Mulatier and S. P. Lacour, *Adv. Mater.*, 2016, 28, 4507–4512.

- 43 K. B. Ozutemiz, J. Wissman, O. B. Ozdoganlar and C. Majidi, Adv. Mater. Interfaces, 2018, 5, 1701596.

- 44 B. Zhang, Q. Dong, C. E. Korman, Z. Li and M. E. Zaghloul, *Sci. Rep.*, 2013, 3, 1098.

- 45 S. Cheng and Z. Wu, Lab Chip, 2010, 10, 3227-3234.

- 46 T. Lu, E. J. Markvicka, Y. Jin and C. Majidi, ACS Appl. Mater. Interfaces, 2017, 9, 22055–22062.

- 47 T. Lu, J. Wissman, Ruthika and C. Majidi, ACS Appl. Mater. Interfaces, 2015, 7, 26923–26929.

- 48 R. D. Sochol, E. Sweet, C. C. Glick, S.-Y. Wu, C. Yang, M. Restaino and L. Lin, *Microelectron. Eng.*, 2018, 189, 52–68.

- 49 Y. Yoon, S. Kim, D. Kim, S. K. Kauh and J. Lee, *Adv. Mater. Technol.*, 2018, 0, 1800379.

- 50 S. Zhu, J.-H. So, R. Mays, S. Desai, W. R. Barnes, B. Pourdeyhimi and M. D. Dickey, *Adv. Funct. Mater.*, 2013, 23, 2308–2314.

- 51 Y. Lin, C. Cooper, M. Wang, J. J. Adams, J. Genzer and M. D. Dickey, *Small*, 2015, **11**, 6397–6403.

- 52 T. Kim and Y. L. Park, *IEEE Robot. Autom. Lett.*, 2018, 3, 881-887.

- 53 A. Robinson, A. Aziz, Q. Liu, Z. Suo and S. P. Lacour, J. Appl. Phys., 2014, 115, 143511.

- 54 M. Tavakoli, C. Benussi and J. L. Lourenco, *Expert Syst. Appl.*, 2017, **79**, 322–332.

- 55 T. Shay, O. D. Velev and M. D. Dickey, *Soft Matter*, 2018, 14, 3296–3303.

- 56 Y. Yu, J. Zhang and J. Liu, PLoS One, 2013, 8, e58771.